# Power Electronics & Drives Board V2

for National Instruments System on Module - sbRIO-9651®

# HARDWARE and USER MANUAL

ped-board.com

# I. Limited Warranty

This document is provided 'as is' and is subject to being changed, without notice, in future editions. For the latest version, refer to <u>ped-board.com</u>.

PED-Board team reviews this document carefully for technical accuracy; however, PED-Board team MAKES NO EXPRESS OR IMPLIED WARRANTIES AS TO THE ACCURACY OF THE INFORMATION CONTAINED HEREIN AND SHALL NOT BE LIABLE FOR ANY ERRORS.

PED-Board warrants that its hardware products will be free of defects in materials and workmanship that cause the product to fail to substantially conform to the applicable PED-Board specifications for one (1) year from the date of invoice.

Trademarks and service marks of third parties are the property of their respective owners.

Do not use in life support and medical applications. In such cases email to support@ped-board.com

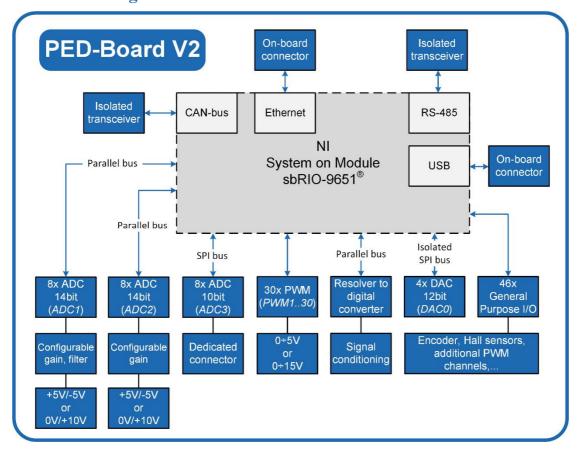

# Power Electronics & Drives Board • PED-Board V2

#### **Applications**

- Power electronics converters and electric drives

- Multilevel converter topologies

- Hybrid power systems

- UPS and PV converters

- High performance control algorithms

- High speed acquisitions and high throughput computation

Fully programmable by LabVIEW®.

Peripherals supported by dedicated LabVIEW® drivers.

Fully editable demo programs.

#### **Features**

- 30 x PWM channels

- $\circ$  0÷15 V or 0÷5V selectable voltage swing

- Direct LED driving capability for optocoupled gate driver

- Additional PWM channels available through the Digital I/O interface

- 14-bit ADC, 8 Channels

- o Simultaneous sampling

- 1.45 μs conversion time, 8 channels

- O Differential input

- o -5V÷5V or 0V÷10V configurable inputs

- Second order low-pass Butterworth active filter with configurable cut-off frequency (factory default 20 kHz)

- 14-bit ADC, 8 Channels

- Simultaneous sampling

- 0 1.45 μs conversion time, 8 channels

- o Differential input

- o -5V÷5V or 0V+10V configurable inputs

- 10-bit ADC, 8 Channels

- o Up to 200 kS/s

- o 0V÷5V input

- 12-bit DAC, 4 Channels

- Digital-to-analog converter with 10 μs settling-time

- Isolated, no ground loops

- Resolver interface

- o Fully configurable electrical interface

- Speed and position measurement

- Resolver fault detection

- 46 x Digital I/O, 3.3V standard

- o Hall-effect position sensors interface

- o Encoder interface

- o Relay control

- o Additional PWM

- o General purpose I/O

- o Additional CAN controller

- Ethernet (programming, debugging and operation)

- 1 x RS-485

- o Isolated transceiver

- o half-duplex and full-duplex communication

- 1 x CAN-bus

- o 2.0A and 2.0B support

- Isolated transceiver

- Up to 1 Mbit/s

- USB port

Custom configuration for scaling circuits, filtering and default setup for orders of 5 units or more.

# Functional block diagram

#### **Table of contents**

| I.    | LIMITED WARRANTY                                      |    |

|-------|-------------------------------------------------------|----|

| II.   | ELECTRICAL SPECIFICATIONS                             | 5  |

| III.  | ANALOG-TO-DIGITAL CONVERTERS                          |    |

| A.    | ADC1 INTERFACE                                        | 5  |

| В.    | ADC2 INTERFACE                                        |    |

| C.    | ADC3 INTERFACE                                        | 8  |

| IV.   | PWM CHANNELS (BUFFERED DIGITAL OUTPUTS)               | 9  |

| ٧.    | DIGITAL-TO-ANALOG INTERFACE                           |    |

| VI.   | RESOLVER INTERFACE                                    | 10 |

| VII.  | CAN-BUS                                               | 11 |

| VIII. | RS-485                                                | 12 |

| IX.   | DIGITAL I/O                                           | 12 |

| D.    | HALL SENSORS INTERFACE AND ENCODER PORT               | 13 |

| X.    | STATUS AND USER LEDS, USER BUTTON AND RESET, USB PORT | 13 |

| XI.   | MECHANICAL DIMENSIONS                                 | 14 |

| XII.  | REFERENCES                                            | 15 |

| XIII. | REVISION HISTORY                                      |    |

#### II. Electrical specifications

| Recommended input voltage supply                   | 12                          | V | Vin - DC           |  |  |

|----------------------------------------------------|-----------------------------|---|--------------------|--|--|

| Input voltage supply range                         | ±10%                        |   | Respect to Vin     |  |  |

| No reverse voltage protection                      |                             |   |                    |  |  |

| Input current                                      | 2.5                         | Α | Max current at Vin |  |  |

| Storage temperature (IEC 60068-2-1, IEC 60068-2-2) | -40 to 85 °C                |   |                    |  |  |

| Operating temperature                              | -25 to 60 °C                |   |                    |  |  |

| Operating humidity (IEC 60068-2-56)                | 10 to 90% RH, noncondensing |   |                    |  |  |

| Storage humidity (IEC 60068-2-56)                  | 5 to 95% RH, noncondensing  |   |                    |  |  |

| Maximum altitude                                   | 5000                        | m |                    |  |  |

| Pollution Degree (IEC 60664)                       | 2                           |   |                    |  |  |

| Analog inputs AINx (ADC1, ADC2) max voltage        | ±11                         | V |                    |  |  |

| Analog inputs AINx (ADC3) max voltage              | 5.1                         | V |                    |  |  |

Do not apply an input voltage higher than 14V at the Vin terminal with respect to GND.

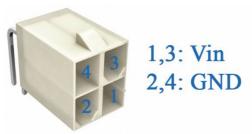

Main power supply and auxiliary connectors

Figure 1. Pinout of the main power connector.

Mate connector DIGIKEY code WM3701-ND, manufacturer Molex. Pin DIGIKEY code WM2501-ND, manufacturer MOLEX.

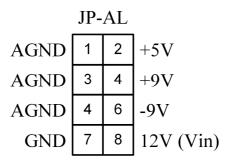

PED-Board is equipped with an auxiliary power connector, which can be used also from the application specific Adapter Board. Pinout is reported in Figure 2, where channels referred to AGND  $(\pm 5V, \pm 9V)$  can provide up to 100mA each one, whereas the 12V link up to 350mA.

Figure 2. Connector for the auxiliary supply.

#### III. Analog-to-Digital converters

Analog to digital interface is based on three separate converters named respectively ADC1, ADC2 and ADC3. ADC1 and ADC2 have their dedicated scaling-filtering input circuit, with detailed explanation illustrated below. ADC3 input are provided with any interfacing hardware leaving to the final user their usage: temperature sensors, etc...

#### A. ADC1 interface

Analog-to-Digital Converter 1 (ADC1) is composed by 8 channels with simultaneous sampling capability and a resolution of 14 bit. Sampling and conversion for the 8 channels take around 1.45µs being capable of 600kS/s.

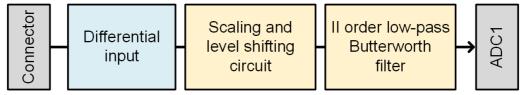

Filtering is performed by a fully configurable differential or single-ended input stage with a second order Butterworth type active filter. Proper measure scaling can be accomplished changing resistor values in the input stage, whereas filtering section exhibit a gain equals to one. Block scheme of ADC1 acquisition chain is shown in Figure 3.

Figure 3. ADC1 measurement chain.

Level shifting circuit is provided to manage both unipolar and bipolar measures. Analog input voltage range is  $\pm 5V$  or 0V to  $\pm 10V$  at the input; whereas maximum operating voltage on the ADC input is  $\pm 5V$ . Provided scaling circuit has an input to output gain  $G_{SC}$  equals to

$$G_{SC} = 1 + \frac{49.4k\Omega}{R_g} \tag{1}$$

where each resistor can be found according to Table 1.

Each analog input is fully differential. Level shifting circuit can be enabled for each analog channel. Bipolar measures are allowed to be sent to ADC in the range of ±5V at the ADC input. In this case 0V input corresponds to 0V at the ADC pin. When unipolar input is desired, 0V at the input terminal corresponds to -5V at the ADC terminal allowing the usage of the converter full scale without resolution deterioration. Selector vs. input is shown in Table 1. When pin 1 and pin 2 are shorted together, resulting measure is unipolar, whereas pin 2 shorted to pin 3 results in bipolar input.

Unipolar / Bipolar 2-3 bip. **Analog input**  $R_g$ 1-2 unip. <u>AIN-1P / A</u>IN-1N  $R_{257}$ JP6 (2-3 default) AIN-2P / AIN-2N JP38 (2-3 default)  $R_{278}$ AIN-3P / AIN-3N JP39 (2-3 default)  $R_{284}$ AIN-4P / AIN-4N JP40 (2-3 default)  $R_{290}$ AIN-5P / AIN-5N  $R_{296}$ JP41 (2-3 default) AIN-6P / AIN-6N  $R_{302}$ JP42 (2-3 default) AIN-7P / AIN-7N  $R_{308}$ JP43 (1-2 default) AIN-8P / AIN-8N JP44 (1-2 default)  $R_{314}$

Table 1 – ADC1 configuring information

Default values are  $R_g$ =not mounted, resulting in a gain of 1. Because of the resulting gain, the full-scale input voltage at the ADC1 connector is  $\pm 5V$  for bipolar arrangement and  $0 \div 10V$  for unipolar configuration.

ADC output data format is in two-complement, independently from the Unipolar/Bipolar scale selection. Retrieved data specifications are highlighted in Table 2. Accordingly, being the ADC resolution equals to 14-bits, resulting data DB[15:14] are set to zero for positive input voltage and one when negative voltage is applied.

Improved code efficiency and reduced FPGA occupancy can be obtained when 14-bits data input is considered using fixed-point signed data type, avoiding to read DB[15:14].

| Description         | Input voltage value at the ADC input pin | Binary and hexadecimal code DB[15:0]          |

|---------------------|------------------------------------------|-----------------------------------------------|

| Positive full scale | +5V                                      | 0b <del>00</del> 01 111 1111 1111<br>0x 1FFF  |

| Negative full scale | -5V                                      | 0b <del>11</del> 10 0000 0000 0000<br>0x E000 |

Table 2 – ADC output data format

The pinout of the ADC1 input connector is shown in Figure 4. Each analog input must be connected between the related input P and N. Signal in converted considering the voltage difference P-N (maximum voltage on each pin is 11V).

|        | JF | P5 |        | JP10   |   |    |        |  |  |

|--------|----|----|--------|--------|---|----|--------|--|--|

| AIN-1P | 1  | 2  | AIN-1N | AIN-5P | 1 | 2  | AIN-5N |  |  |

| AIN-2P | 3  | 4  | AIN-2N | AIN-6P | 3 | 4  | AIN-6N |  |  |

| AIN-3P | 5  | 6  | AIN-3N | AIN-7P | 5 | 6  | AIN-7N |  |  |

| AIN-4P | 7  | 8  | AIN-4N | AIN-8P | 7 | 8  | AIN-8N |  |  |

| AGND   | 9  | 10 | AGND   | AGND   | 9 | 10 | AGND   |  |  |

Figure 4. ADC1 connectors.

#### • ADC1 filtering section

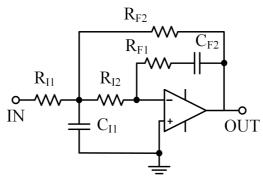

Filtering section of ADC1 is accomplished by a II-order low-pass Butterworth type active filter, being based on the well-known multiple-feedback topology. PED-Board is shipped with a filter cut-off frequency set to 20kHz<sup>1</sup>.

Please refer to Linear Technologies LT1359CS14 integrated circuit for frequency limitations and detailed filter characteristics.

When the filter cut-off frequency needs to be changed, please refer to the following information that are related to the PED-Board components that must be replaced. Each filter has the scheme shown in Figure 5 whereas the relation between the general element and the PED-Board component designator is reported in Table 3.

Figure 5. General electrical scheme of the II order Butterworth filter.

$Table\ 3-Board\ designators\ for\ the\ filter\ components$

| ADC1 channel | $R_{II}$         | $R_{I2}$         | C11              | R <sub>F1</sub> | R <sub>F2</sub>  | CF2       |

|--------------|------------------|------------------|------------------|-----------------|------------------|-----------|

| AIN-1        | R <sub>97</sub>  | R <sub>99</sub>  | $C_{139}$        | Don't change    | R <sub>228</sub> | $C_{137}$ |

| AIN-2        | $R_{102}$        | $R_{103}$        | $C_{143}$        | //              | R <sub>229</sub> | $C_{141}$ |

| AIN-3        | $R_{107}$        | $R_{106}$        | C <sub>146</sub> | //              | R <sub>231</sub> | $C_{142}$ |

| AIN-4        | $R_{101}$        | $R_{100}$        | $C_{140}$        | //              | R <sub>230</sub> | $C_{138}$ |

| AIN-5        | $R_{130}$        | $R_{131}$        | $C_{173}$        | //              | $R_{232}$        | $C_{171}$ |

| AIN-6        | R <sub>134</sub> | $R_{135}$        | $C_{177}$        | //              | R <sub>233</sub> | $C_{175}$ |

| AIN-7        | R <sub>139</sub> | $R_{138}$        | $C_{180}$        | //              | R <sub>235</sub> | $C_{176}$ |

| AIN-8        | R <sub>133</sub> | R <sub>132</sub> | C <sub>174</sub> | //              | R <sub>234</sub> | $C_{172}$ |

# B. ADC2 interface

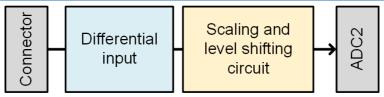

ADC2 interface is similar to the previously depicted ADC1, except for the low-pass filtering path that is avoided to have full bandwidth. Signal conditioning chain is highlighted in Figure 6. Input circuit devoted to scaling and level shifting exhibits the same gain as shown in (1). Each analog input is configured as differential. Moreover, all channels can be configured independently for unipolar or bipolar input. Detailed information are available in Table 4.

<sup>&</sup>lt;sup>1</sup> Custom filter configuration available for orders of 5 or more units.

Figure 6. ADC2 measurement chain.

Table 4 – ADC2 configuring information

|                   |                  | Unipolar  | / Bipolar  |

|-------------------|------------------|-----------|------------|

| Analog input      | $R_{ m g}$       | 1-2 unip. | 2-3 bip.   |

| AIN-9P / AIN-9N   | $R_{320}$        | JP46 (2-2 | 3 default) |

| AIN-10P / AIN-10N | $R_{326}$        | JP46 (2-2 | 3 default) |

| AIN-11P / AIN-11N | $R_{332}$        | JP47 (2-2 | 3 default) |

| AIN-12P / AIN-12N | R <sub>338</sub> | JP48 (2-2 | 3 default) |

| AIN-13P / AIN-13N | R <sub>344</sub> | JP49 (2-2 | 3 default) |

| AIN-14P / AIN-14N | $R_{350}$        | JP50 (2-2 | 3 default) |

| AIN-15P / AIN-15N | R <sub>356</sub> | JP51 (1-2 | 2 default) |

| AIN-16P / AIN-16N | R <sub>362</sub> | JP52 (1-2 | 2 default) |

Default values are  $R_{g1}=27.4k\Omega$ ,  $R_{g2}=3.3k\Omega$  with 1% accuracy, resulting in a gain of 0.927.

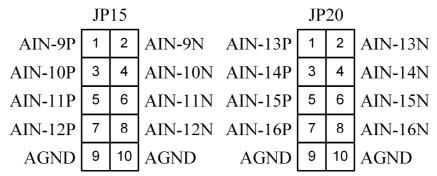

ADC2 inputs are available on the PED-Board with reference to the pinout shown in Figure 7.

Figure 7. ADC2 connectors.

#### C. ADC3 interface

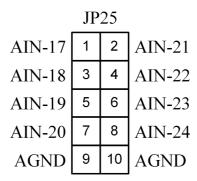

Analog interface ADC3 is capable of low resolution, up to 200kS/s measures acquisition. Digitalization is performed by 10-bit on the available 8 channels. A SPI bus performs communication between the ADC3 and NI sbRIO-9651. ADC3 inputs are available on the JP25 connector having the pinout shown in Figure 8. Analog input voltage swing is unipolar from 0V to +5V. At +5V the resulting output code is  $2^{10}$ -1. No signal conditioning or scaling is provided for ADC3 inputs.

Figure 8. ADC3 connector.

# IV. PWM channels (Buffered Digital Outputs)

Up to 30 independent PWM channels are provided through the connectors JP33, JP34, JP35 and JP36 having the detailed pinout of Figure 9. Each channel that is composed by 10 PWM, can be configured to provide 0÷15 V or 0÷5 V voltage swing. When 0÷5V is selected, the PWM pin can drive directly the input LED of a classical opto-coupled gate driver, such as ACPL-333J or HCPL-316.

Voltage selection can be configured by JP2, JP3 and JP4 selectors. Connecting pin 2 to pin 1, each group is supplied from the on-board +5V with 15mA continuous current capability on each PWM output. Whereas connecting pin 2 to pin 3, PWM voltage swing is 0÷15V with 5mA continuous current on each PWM channel. JP2 controls PWM1 to PWM10, JP3 is related to PWM11 to PWM20 and finally JP4 configures PWM21 to PWM30, as summarized in Table 5. PWM buffer circuit is non-inverting.

|        | JP | 36 |        |        | JР | 35 |        |        | JP | 34 |        |       | JP | 33 |        |

|--------|----|----|--------|--------|----|----|--------|--------|----|----|--------|-------|----|----|--------|

| DGND   | 1  | 2  | DGND   | DGND   | 1  | 2  | DGND   | DGND   | 1  | 2  | DGND   | DGND  | 1  | 2  | DGND   |

| PWM-21 | 3  | 4  | PWM-22 | PWM-29 | 3  | 4  | PWM-30 | PWM-17 | 3  | 4  | PWM-18 | PWM-5 | 3  | 4  | PWM-6  |

| PWM-23 | 5  | 6  | PWM-24 | PWM-11 | 5  | 6  | PWM-12 | PWM-19 | 5  | 6  | PWM-20 | PWM-7 | 5  | 6  | PWM-8  |

| PWM-25 | 7  | 8  | PWM-26 | PWM-13 | 7  | 8  | PWM-14 | PWM-1  | 7  | 8  | PWM-2  | PWM-9 | 7  | 8  | PWM-10 |

| PWM-27 | 9  | 10 | PWM-28 | PWM-15 | 9  | 10 | PWM-16 | PWM-3  | 9  | 10 | PWM-4  | ·     |    |    | •      |

Figure 9. PWM connectors.

Table 5 – PWM voltage swing configuration<sup>2</sup>

|              | PWM1PWM10<br>(JP2) | PWM11PWM20<br>(JP3) | PWM21PWM30<br>(JP4) |

|--------------|--------------------|---------------------|---------------------|

| Position 1-2 | +5 V (default)     | +5 V (default)      | +5 V                |

| Position 2-3 | +15 V              | +15 V               | +15 V (default)     |

Additional PWM outputs can be achieved from the *Digital I/O* pins, implementing the voltage and current driving circuits directly on the application specific Adapter Board.

When each PWM channel needs to be controlled by a dedicated algorithm, NI sbRIO-9651 pins can be directly accessed using the following information (Table 6).

Table 6 – PED-Board and sbRIO-9651 PWM pin routing

| PED-<br>Board | sbRIO-9651  | PED-<br>Board | sbRIO-9651  | PED-<br>Board | sbRIO-<br>9651 |

|---------------|-------------|---------------|-------------|---------------|----------------|

| PWM-1         | DIO_33_N    | PWM-11        | DIO_31      | PWM-21        | DIO_56_N       |

| PWM-2         | DIO_33      | PWM-12        | DIO_38_MRCC | PWM-22        | DIO_59         |

| PWM-3         | DIO_30      | PWM-13        | DIO_28_N    | PWM-23        | DIO_59_N       |

| PWM-4         | DIO_37_MRCC | PWM-14        | DIO_31_N    | PWM-24        | DIO_62_N       |

| PWM-5         | DIO_29      | PWM-15        | DIO_37_N    | PWM-25        | DIO_28         |

| PWM-6         | DIO_29_N    | PWM-16        | DIO_39_N    | PWM-26        | DIO_50_N       |

| PWM-7         | DIO_36_SRCC | PWM-17        | DIO_34      | PWM-27        | DIO_53         |

| PWM-8         | DIO_36_N    | PWM-18        | DIO_39_SRCC | PWM-28        | DIO_53_N       |

| PWM-9         | DIO_32_N    | PWM-19        | DIO_30_N    | PWM-29        | DIO_35_N       |

| PWM-10        | DIO_32      | PWM-20        | DIO_34_N    | PWM-30        | DIO_38_N       |

-

<sup>&</sup>lt;sup>2</sup> Custom configuration available for orders of 5 or more units.

#### V. Digital-to-Analog interface

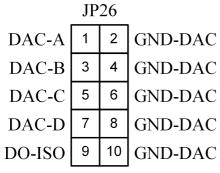

Digital to analog interface is based on a fast, low settling time converter with SPI interface. Output voltage, which swings from 0V to +5V, is isolated from the board ground, allowing to drive directly any output circuit avoiding ground loops. DAC resolution is 12 bit, starting from 0 to 4095 where the full output voltage is available. DAC connector shown in Figure 10 provide also one isolated digital output channel, DO-ISO. DAC and DO-ISO are on the same ground.

For faster usage of the DAC outputs, even with reduced channels, the connector shown in Figure 11 is provided. Mate connector DIGIKEY code ED10556-ND.

Figure 10. Connector for DAC and Digital-Out pin.

Figure 11. DAC connector.

#### VI. Resolver interface

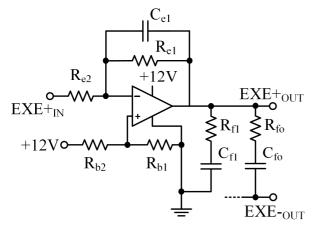

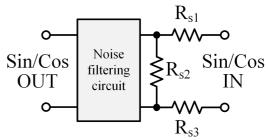

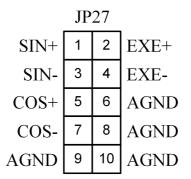

Resolver interface is mainly based on the Analog Devices AD2S1205YST integrated circuit. Differential excitation is provided with on-board current buffer. Sin/Cos acquiring circuits are designed to accomplish different type of resolvers, being equipped with a dedicated scaling circuit that can be configured by simply replacing some resistors. Carrier signal amplitude regulation is also allowed with a maximum peak voltage of 10V. Excitation driving circuit is able to directly supply resolvers based on rotary transformer or switched reluctance architecture. Scheme of the excitation circuit is shown in Figure 12 and it is reported in [1]. Both carrier signals, EXE+ and EXE- have the same amplification circuit. Detailed information on how to select the circuit component can be found in [1]. Resolver Sin/Cos acquiring circuit is shown in Figure 13, where three input resistors can be used to properly scale the resolver return signals. With reference to the PED-Board, Sin signal resistors are  $R_{s1}=R_{182}$ ,  $R_{s2}=R_{183}$  and  $R_{s3}=R_{186}$ . Accordingly, Cos resistors are  $R_{s1}=R_{191}$ ,  $R_{s2}=R_{192}$  and  $R_{s3}=R_{195}$ . More info can be found on Table 7 where the default values are also indicated. If the component value is not specified it stands for 'not mounted'. Resolver signals can be accessed by the JP27 connector as shown in Figure 14.

Table 7 – Resolver circuit components<sup>3</sup>

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                         |                   | EXE+                           | EXE-                           |          | Sin                             | Cos                             |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|--------------------------------|--------------------------------|----------|---------------------------------|---------------------------------|

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                         | R <sub>e1</sub>   | $R_{197} (24 \text{ k}\Omega)$ | $R_{199} (24 \text{ k}\Omega)$ | $R_{s1}$ | $R_{182} (5.6 \text{ k}\Omega)$ | $R_{191} (5.6 \text{ k}\Omega)$ |

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                         | R <sub>e2</sub>   | $R_{236} (15 \text{ k}\Omega)$ | $R_{238} (15 \text{ k}\Omega)$ | $R_{s2}$ | $R_{183} (12 \text{ k}\Omega)$  | $R_{192} (12 \text{ k}\Omega)$  |

| $\begin{array}{c cccc} C_{e1} & C_{324} & C_{325} \\ \hline R_{f1} & R_{239} & R_{240} \\ \hline C_{f1} & C_{327} & C_{328} \\ \hline R_{fo} & R_{237} \\ \hline \end{array}$ | $R_{b1}$          | R <sub>241</sub> (1            | l2 kΩ)                         | $R_{s3}$ | $R_{186} (5.6 \text{ k}\Omega)$ | $R_{195} (5.6 \text{ k}\Omega)$ |

| $\begin{array}{c cccc} R_{\rm fl} & R_{239} & R_{240} \\ \hline C_{\rm fl} & C_{327} & C_{328} \\ \hline R_{\rm fo} & R_{237} & \\ \hline \end{array}$                        | $R_{b2}$          | R <sub>243</sub> (2            | 27 kΩ)                         |          |                                 |                                 |

| $\begin{array}{ c c c c c }\hline & C_{fl} & C_{327} & C_{328} \\\hline & R_{fo} & R_{237} \\\hline \end{array}$                                                              | $C_{e1}$          | $C_{324}$                      | $C_{325}$                      |          |                                 |                                 |

| $R_{\rm fo}$ $R_{237}$                                                                                                                                                        | $R_{\rm fl}$      | R <sub>239</sub>               | $R_{240}$                      |          |                                 |                                 |

|                                                                                                                                                                               | $C_{\mathrm{fl}}$ | $C_{327}$                      | $C_{328}$                      |          |                                 |                                 |

| C <sub>5</sub> , C <sub>226</sub>                                                                                                                                             | $R_{fo}$          | $R_{237}$                      |                                |          |                                 |                                 |

| C10 C320                                                                                                                                                                      | $C_{\mathrm{fo}}$ | C                              | 326                            |          |                                 |                                 |

<sup>&</sup>lt;sup>3</sup> Custom resolver configuration available for orders of 5 or more units.

Figure 12. Electrical scheme of the resolver excitation circuit.

Figure 13. Resolver Sin/Cos scaling and acquiring circuit.

Figure 14. Resolver connector.

#### VII. CAN-bus

Isolated CAN transceiver having an operating data rate up to 1 Mbit/s has been integrated on the PED-Board. LabVIEW CLIP can straightforwardly realize the CAN controller if needed. However, it takes some FPGA resources resulting in an average estimation around 5.9% of Slice Registers, 12.5% of Slice LUTs and 10% of Block RAMs. No DSP48s resources are taken to implement the CAN controller. CAN connector is provided as shown in Figure 15. Mate connector DIGIKEY code ED10556-ND.

Figure 15. Fast CAN-bus connector

When CAN communication is not needed, FPGA space can be saved by removing the CAN controller from the generated CLIP.

CLIP generation requires the information concerning the sbRIO-9651 pins to be used as CAN TX and RX. Provided PED-Board CAN controller is connected as in Table 8.

Table 8 - Pin routing between the CAN-Bus transceiver and the sbRIO-9651

| PED-Board | sbRIO-9651 |

|-----------|------------|

| CAN_TX    | DIO_8      |

| CAN_RX    | DIO_9      |

R213 is used to setup the slope of the CAN-bus data (default  $0 \Omega$ ). 120  $\Omega$  termination resistor can be inserted if needed, by closing the jumper JCAN.

#### • II CAN controller

A second CAN-bus controller can be implemented by the LabVIEW CLIP generator and it will be available to the Digital I/O pins. The required transceiver must be placed directly on the *Adapted Board*.

#### **VIII. RS-485**

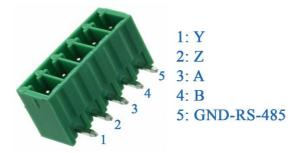

RS-485 port can be generated by the LabVIEW CLIP Generator. PED-Board is equipped with an isolated transceiver and a dedicated connector M3 having the pinout shown in Figure 16.

RS-485 CLIP can be generated according to the pin routing shown in Table 9.

Each TX and RX channel has its own  $120 \Omega$  termination resistor, which can be inserted by closing the jumper J485-H for RX and J485-F for TX. In case of half-duplex mode of operation, only one termination resistor should be closed.

Figure 16. RS-485 connector.

Table 9 – Pin routing between the RS-485 transceiver and the sbRIO-9651

| PED-Board   | sbRIO-9651  |                           |

|-------------|-------------|---------------------------|

| RS485_TX_EN | DIO_11      | Transceiver TX enable pin |

| RS485_TX    | DIO_12      | Transceiver TX pin        |

| RS485_RX    | DIO_14      | Transceiver RX pin        |

| RS485_RX_EN | DIO_15_MRCC | Transceiver RX enable pin |

# IX. Digital I/O

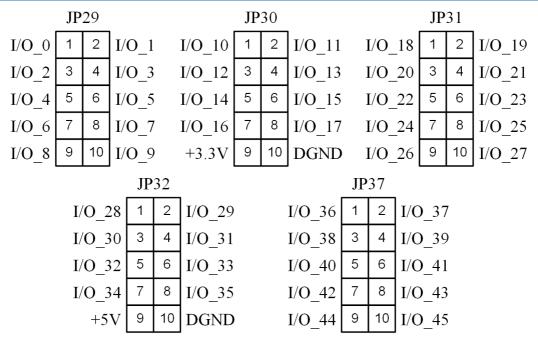

Additional I/O pins are available through JP29, JP30, JP31, JP32 and JP37 connectors that allow to route those pins directly to the *Adapter Board*. Connectors' pinout is highlighted in Figure 17. Digital I/O are directly connected to the ZYNQ-7020 pins, refers to the Xilinx device data-sheet for the electrical specifications.

Provided additional Digital I/O pins are directly connected to the sbRIO-9651 FPGA pins. According to the National Instruments sbRIO-9651 data-sheet, the relation between the PED-Board and sbRIO-9651 pins is as in Table 10.

Figure 17. Digital I/O connectors.

| PED-   | sbRIO-   | PED-   | sbRIO-   | PED-   | sbRIO-   | PED-   | sbRIO-   |

|--------|----------|--------|----------|--------|----------|--------|----------|

| Board  | 9651     | Board  | 9651     | Board  | 9651     | Board  | 9651     |

| I/O_0  | DIO_25_N | I/O_12 | DIO_24   | I/O_24 | DIO_49_N | I/O_36 | DIO_19_N |

| I/O_1  | DIO_0    | I/O_13 | DIO_21   | I/O_25 | DIO_46_N | I/O_37 | DIO_72_N |

| I/O_2  | DIO_25   | I/O_14 | DIO_24_N | I/O_26 | DIO_70   | I/O_38 | DIO_69_N |

| I/O_3  | DIO_1    | I/O_15 | DIO_43_N | I/O_27 | DIO_46   | I/O_39 | DIO_44_N |

| I/O_4  | DIO_22   | I/O_16 | DIO_47   | I/O_28 | DIO_70_N | I/O_40 | DIO_47_N |

| I/O_5  | DIO_19   | I/O_17 | DIO_43   | I/O_29 | DIO_67_N | I/O_41 | DIO_2    |

| I/O_6  | DIO_22_N | I/O_18 | DIO_48   | I/O_30 | DIO_71   | I/O_42 | DIO_3    |

| I/O_7  | DIO_20_N | I/O_19 | DIO_44   | I/O_31 | DIO_67   | I/O_43 | DIO_4    |

| I/O_8  | DIO_23   | I/O_20 | DIO_48_N | I/O_32 | DIO_71_N | I/O_44 | DIO_5    |

| I/O_9  | DIO_20   | I/O_21 | DIO_45_N | I/O_33 | DIO_68_N | I/O_45 | DIO_6    |

| I/O_10 | DIO_23_N | I/O_22 | DIO_49   | I/O_34 | DIO_72   |        |          |

| I/O 11 | DIO 21 N | I/O 23 | DIO 45   | I/O 35 | DIO 68   |        |          |

Table 10. PED-Board vs. sbRIO-9651 digital I/O pins

# D. Hall sensors interface and Encoder port

PED-Board is equipped with a digital interface for glue less connection of low-resolution hall-effect position sensors. These can be connected to the pins provided by the Digital I/O port, JP29, JP30, JP31, JP32 and JP37. As shown in Figure 17, non-isolated +3.3V and +5V auxiliary supplies are provided, which can be used to directly feed hall-sensors and encoders with a maximum available current of 100mA each one.

# X. Status and User LEDs, User button and Reset, USB port

PED-Board is equipped with three LEDs related to the sbRIO-9651 operation, POWER (green), STATUS (yellow) and TEMP (red). Please refer to the National Instruments System-On-Module data-sheet for detailed explanation.

Additional user LEDs are provided, which can be controlled directly from the sbRIO-9651: LED1 (green) connected to the pin DIO\_75 and LED2 (green) connected to DIO\_81.

NI sbRIO-9651 can be reset by pressing SW1. SW2 can be used as user switch, having normally low state. It is connected to the DIO 87 SRCC pin of the sbRIO-9651 board.

USB port, formally USB1, can act only as HOST port.

#### XI. Mechanical dimensions

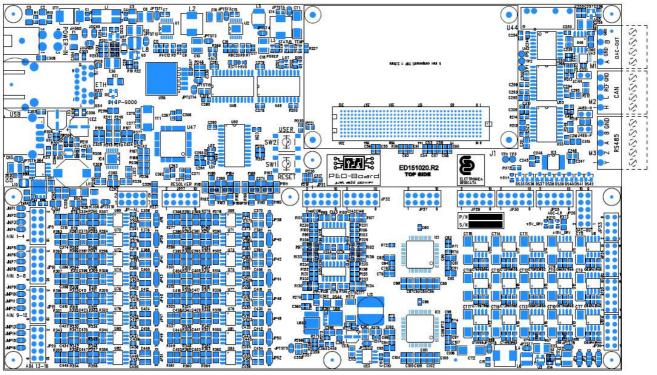

PED-Board V2 size is 220mm x 130mm, same as the previous PED-Board system. Mounting holes have not been changed.

Figure 18. PED-Board mechanics.

Application specific Adapter Board must be placed above the board-to-board connectors, i.e. in the PED-Board bottom rectangle shown in Figure 18.

# XII. References

[1] Jakub Szymczak, Shane O'Meara, Johnny S. Gealon, and Christopher Nelson De La Rama, "Precision Resolver-to-Digital Converter Measures Angular Position and Velocity", Analog Devices application note.

# **XIII. Revision history**

| Date | Rev# |  |

|------|------|--|

|      |      |  |

|      |      |  |

|      |      |  |

#### Contacts

E.D. ELETTRONICA DEDICATA S.r.l. Via dell'Industria 29/31, 25032 Chiari (BS) Italy tel. +39 030 7281715

Support support@ped-board.com

Quote and purchase purchase@ped-board.com

General info info@ped-board.com